## AIST RESEARCH HOT LINE

## SiCホモエピタキシャルウエハにおけるオフ角低減を実現次世代パワー半導体 SiC ウエハ作制

## 炭化珪素(SiC)を用いた半導体素子はSiを超 える超低損失のパワー素子を実現できるもの として期待されており、近年その開発が精力 的に進められている。SiC半導体素子は、バ ルクSiC結晶基板の上に膜厚、不純物濃度を 高度に制御して成長させた薄膜(ホモエピタキ シャルウエハ)上に作製される。そのため、エ ピタキシャルウエハの品質は、作製された半 導体素子の特性に大きく影響することにな る。SiCは、SiとCの積層様式が多様に変化し やすい(結晶多形)半導体結晶である。従っ て、多形の混入がなく、パワー半導体に適し た多形の一つである4H-SiCだけのエピタキ シャル膜を得ることは素子作製上の必要不可 欠な技術である。そのために今日では積層情 報を伝えられるようにSi原子が最表面にある Si面を結晶軸に対して数度傾けた(オフ角と言 う)オフ基板上にエピタキシャル膜を作製する 手法が開発されており、それが必然とされて いる。

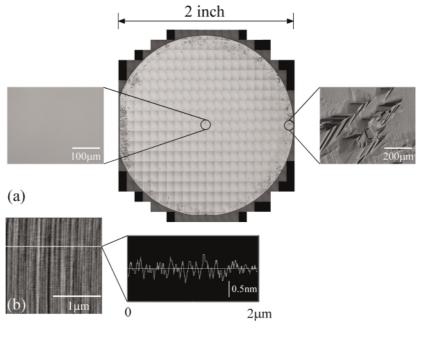

一方で、ウエハにオフ角をつけると、オフ 角に対応したミクロには異なる方位の結晶面 (ステップ:階段状の形態)が現れるようにな る。そのミクロな段差によりパワー素子に重 要な半導体/酸化膜界面が乱れるといった問題 が指摘されており、ウエハのオフ角の低減が 求められている。しかし、Si面では基板のオ フ角を小さくするとエピタキシャル成長時に ステップバンチング(ステップの粗密化)によ り表面の平坦性が失われやすくなるという問 題がある。一方、4H-SiCのバルク成長では成 長手法は異なるが、Si面とは反対にC原子が 最表面にあるC面で結晶成長を行うことによ り4H-SiCを安定して成長させ得ることが知ら れている。我々はこの事実に着目し、C面を 用いることによって4H-SiCエピタキシャル膜 のオフ角低減の可能性を追求した。その結 果、エピタキシャル成長条件を最適化するこ とによって、図に示すようにオフ角0.5°の2イ ンチ4H-SiC基板においてウエハエッジ近傍以 外は表面が原子レベルの平坦性を持ち、他の SiC多形の混入がないエピタキシャルウエハ を成長させることに成功した。

これにより、技術的にはこれまでウエハに存在していたオフ角に起因する素子特性上の問題が改善される見通しが得られるとともに、一部の国で有効とされているオフ基板成長に対する特許主張の懸念が払拭されるものと思われる。本成果により、SiCを用いたパワー半導体素子の開発に一層の拍車がかかるものと期待される。

児島一聡 kazu-kojima@aist.go.jp パワーエレクトロニクス研究センター

図 エピタキシャルウエハの表面状態 (a)微分干渉顕微鏡像、(b)原子間力顕微鏡像

## 関連情報

● 児島一聡 等: 第 64 回応用物理学会学術講演会, 講演予稿集, 1a-B-2.