## 開超低損

## 電力エネルギーを有効利用することは、環境保全、資源の節約の両面からますます重要となっている。この中で、電力変換時に発生する損失を極力低減することは重要な課題の一つである。電力変換にはパワー半導体デバイスが広く用いられているが、既存のシリコン(Si)パワーデバイスは物性値からくる性能限界に近づきつつあり、これ以上の損失低減は期待できない。これに対して、ワイドギャップ半導体であるシリコンカーバイド(4H-SiC)はSiに比ベバンドギャップが約3倍、絶縁破壊電界強度が7倍、熱伝導率が3倍と大きく、理論的には通電時の損失(オン抵抗)をSiパワーデバイスの1/200まで

に低減できるとされている。

縦型パワーMOSFETの半導体基板を従来の Siから4H-SiCに変更すれば、超低損失パワース イッチングデバイスが実現できると考えられ ている。しかしながら、現在までに試作され ている4H-SiC縦型MOSFETは、Siの理論限界 を超えるものはいくつか存在するものの、SiC の特性が十分に発揮されるに至っていない。 これはMOSゲートを形成するSiO<sub>2</sub>/SiC界面に おけるチャンネル移動度が理想値に比べはる かに低いことが原因となっている。この問題 の一部は不純物のドーピング過程に起因して いる。即ち、SiCへの不純物ドーピングは熱拡 散が困難であるためイオン注入法を用いてい るが、この場合チャンネルとなるアクセプタ 不純物領域(Pウェル)を活性化するためには 1700℃以上の熱処理が必要となる。したがっ

て表面の結晶性が劣化しやすく、高い移動度 が得られないという欠点が生じていた。

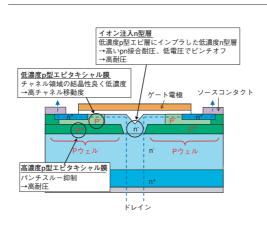

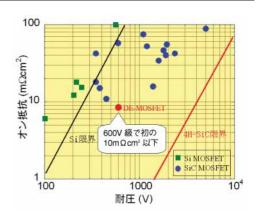

我々はこの問題に対して、Pウェルを結晶品 質に優れたエピタキシャル成長膜によって形 成する4H-SiC縦型MOSFETの構造および作製 プロセスを開発した。この構造の特徴はPウェ ルが濃度の異なる二重のエピタキシャル成長 膜によって構成されていることから、二重エ ピタキシャル縦型MOSFET (Double-Epitaxial MOSFET)と名付けた。図1にその断面構造を 示す。Pウェルの下層はソース・ドリフト層間 のパンチスルーを抑制するために高濃度膜と なっており、上層は高いチャンネル移動度を 得るために低濃度膜となっている。また、P ウェル領域間のドナー不純物領域は低電圧で ピンチオフできるように低濃度のイオン注入 によって形成されている。以上のような構造 をとることによって高い耐電圧と低いオン抵 抗の両立が可能となった。図2は本研究で開 発したDE-MOSFETとこれまでに報告された MOSFETの耐電圧とオン抵抗の関係を示して いる。600Vの耐電圧を持つDE-MOSFETのオ ン抵抗は8.5mΩcm²を示し、同じ耐電圧を持つ Si-MOSFETに比べて10分の1以下に低減され ている。この結果は、汎用性の高い600V級パ ワーMOSFETにおける壁であったオン抵抗 10mΩcm<sup>2</sup>以下を世界で初めて達成したことに なり、4H-SiCパワーデバイス実用化に向けて の大きな一歩になったといえる。

はらだしんすけ 原田信介 s-harada@aist.go.jp パワーエレクトロニクス研究センター

図1 二重エピタキシャル縦型MOSFET (DE-MOSFET) の断面構造

図2 開発した DE-MOSFET とこれまでに報告 された MOSFET の耐電圧とオン抵抗の関係

## 関連情報

- 1) S. Harada, M. Okamoto, T. Yatsuo, K. Adachi, K. Suzuki, S. Suzuki, K. Fukuda, K. Arai: 10th International Conference on Silicon Carbide and Related Materials (2003).

- 2) 原田信介, 岡本光央, 八尾勉, 安達和広, 福田憲司, 荒井和雄: SiC 及び関連ワイドギャップ半導体研究会第 12 回講演会 (2003).