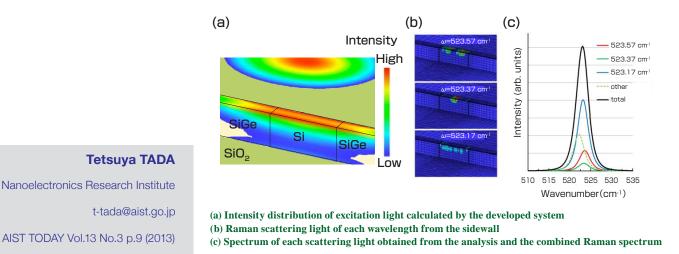

## Three-dimensional stress analysis simulator for ultra-small silicon devices Analysis at nanometer level using an optical microscope

We have developed a three-dimensional stress analysis simulator for ultra-small silicon (Si) devices. The developed simulation technology allows the analysis of the distribution of the mechanical stress (or mechanical strain) applied to ultra-small Si devices with a spatial resolution at the nanometer level by calculating the modulation of light intensity distribution caused by the device structure in the micro-Raman spectroscopy measurement using an optical microscope.

Information Technology and Electronics

## High performance transistors on polymer A back-end integration technology for post-silicon materials

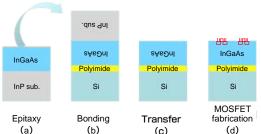

We have developed a technology for the transfer of a high performance compound semiconductor layer onto a silicon substrate using an inexpensive heat-resistant polymer as an adhesive. Transistors superior to silicon transistors were fabricated at maximum process temperatures as low as 400  $^{\circ}$ C on the polymer. Using the layer transfer and low-temperature device fabrication technologies, the realization of high-performance, multifunction devices integrating post-silicon materials with silicon large-scale integrated circuits is expected.

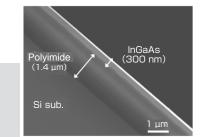

Tatsurou MAEDA Nanoelectronics Research Institute t-maeda@aist.go.jp AIST TODAY Vol.13 No.3 p.10 (2013)

Cross-sectional SEM image of InGaAs layer on polyimide Fabrication method of transistors on polyimide